Funkamateur 12/87 |

Durch die rasche Entwicklung der Mikrorechentechnik und der Bauelemente

besteht auch für den Elektronikamateur die Möglichkeit,

seinen Kleincomputer zu einem attraktiven Arbeitsmittel auszubauen.

Dabei ist die Verbesserung des Kleincomputers vor allem

hinsichtlich seines Speicherbereichs zu sehen, so daß dann mit

größeren BASIC-Programmen gearbeitet werden kann.

Im Beitrag soll eine Speichererweiterung für den Amateurcomputer

"AC1" vorgestellt werden. Dabei sollen die dynamischen

RAM U 2164 D zum Einsatz kommen. Mit acht Stück U 2164 D

läßt sich der volle, adressierbare Speicherbereich der ZVE U

880 D

ausnutzen. Lediglich die Adressen des "AC1" von 0000H bis 1FFFH werden

durch diese Erweiterung nicht selektiert, da sie bereits

durch das Grundmodul belegt sind. Das aber ist kein Verlust von 8

KByte, sondern es ist denkbar, diese 8 KByte später als

Hintergrundspeicher zu nutzen.

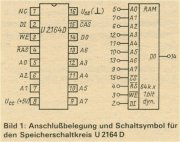

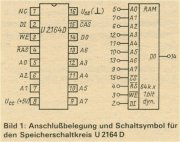

Der U 2164 D ist ein dynamischer RAM-Schaltkreis,

der zu 64 K x 1 Bit organisiert ist. Für die Wortbreite eines

Datenbusses

werden also acht Stück dieser IS benötigt. Gegenüber dem

dynamischen RAM U 256 D ist der Einsatz unkomplizierter, da nur eine

Betriebsspannung von + 5 V erforderlich ist. Es entfallen also

Schutzmaßnahmen zur Verhütung von Schaltkreisschäden

durch das

Fehlen der -5-V-Spannung. Hier einige technische Angaben zum U 2164 D

nach [1]:

- dynamischer RAM, Refreshzeit = 2 ms, 128 Refreshzyklen;

- Speicherkapazität 64 Kbit, bitorgan.;

- Zugriffszeit von /RAS ist tRAC = 200 ns;

- Zugriffszeit von /CAS ist tCAC = 115 ns;

- eine Betriebsspannung Ucc = + 5 V;

- Tristate-Ausgangsstufen;

- 16poliges DIL-Gehäuse.

Auf die Arbeitsweise des U 2164 D sei hier nicht weiter eingegangen,

sie wurde anhand des U 256 D in [2]

ausführlich beschrieben.

Unterschiede gibt es hauptsächlich durch den größeren

Speicherbereich, ansonsten bestehen viele Ähnlichkeiten zwischen

beiden

Bausteinen. Wichtig ist, daß entgegen den Gewohnheiten am Pin 8 (Ucc)

+ 5 V anliegt und am Pin 16 (Uss) Masse. Die Anschlußbelegung

ist im Bild 1 dargestellt.

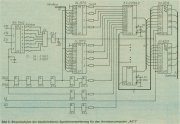

Ausgangspunkt war die Schaltung in [3].

Der Adreßbereich von 64 KByte wird durch den Dekoder MH 7442 in

8-KByte-Schritte

unterteilt. Dadurch ist es möglich, z.B. EPROM-Adressen, die schon

im System liegen, auszublenden bzw. einzelne

Speicherbereiche abzuschalten. Alle erforderlichen CS-Signale gelangen

über Brücken an das NAND-Gatter D 130 D. Nach

einer Negation am Gatter D2.3 wird der Treiber DS 8216 D am /OE-Eingang

selektiert. Dadurch, daß man Daten eines RAMs sowohl

lesen als auch einschreiben muß, erfolgt durch die ZVE eine

Umschaltung in den Lesezustand durch /RD = L-Potential,

/WR hat H-Potential. Soll geschrieben werden, tauschen die Signale /RD

und /WR ihre logischen Zustände, also /RD = H und /WR = L.

/RD bestimmt die Richtung des Datentransports der DS 8216 D; so

schaltet /RD = L die Speicherausgänge (DO) auf den Datenbus,

bei /WR = H wird gelesen. /RD = H legt die Speichereingänge (DI)

auf den Datenbus. Wird dann /WR = L, kann ein Schreiben in den

Speicher erfolgen.

Das erforderliche /RAS-Signal entsteht durch /MREQ. Um eine zu

große Belastung des /MREQ-Signals der ZVE zu vermeiden,

verstärken

die Gatter D3.1 und D3.2 das Signal, das erst dann an die

/RAS-Eingänge der acht U 2164 D gelangt. Da das /CAS-Signal

zeitlich

später als das /RAS-Signal am U 2164 D liegen muß, wird es

aus dem /MREQ über eine Verzögerungskette aus sechs Gattern

gewonnen.

Am Ausgang des Gatters D1.4 liegt das Multiplexsignal für die zwei

Adreßmultiplexer DL 257 D. Der Eingang des Gatters D2.2

erhält das /RFSH-Signal der ZVE U 880 D, um ein ständiges

Auffrischen des Speicherinhalts der dRAMs zu gewährleisten.

Die Eingänge der DL 257 D sind mit dem Adreßbus verbunden

(A0 bis A15).

Es ist besonders darauf zu achten, daß die niederwertigen

Adressen nicht vertauscht werden, da es dann nicht zu einem eindeutigen

"Refresh" kommt, der Speicher "vergißt" dann. Die Ausgänge

sind zur Pegelanpassung über Widerstände von

33 Ω mit den Adressen des U 2164 D verbunden. Die Datenausgänge

liegen an den Y-Eingängen bzw. die Dateneingänge an

den A-Eingängen des DS 8216 D. Die Ausgänge der Treiber des

DS 8216 D (B1 bis B4 sowie B1' bis B4') sind direkt mit dem

Datenbus des Rechners verbunden. Wichtig ist es, alle U 2164 D mit

einem Kondensator von 100 nF von + 5 V gegen Masse jeweils abzublocken.

Diese sollen

Störimpulse, die beim Lesen oder Beschreiben der RAMs auftreten,

unterdrücken.

Der Aufbau der Schaltung

erfolgte auf einer Universalleiterplatine 170 mm x 95 mm. Sie wurde

handverdrahtet und funktioniert

problemlos. Alle Anschlüsse des U 2164 D sind bis auf die

Dateneingänge (DI) und die Datenausgänge (DO) in gleicher

Weise

beschaltet. Besonderer Wert ist auf eine saubere und kurze Verdrahtung

der Adressen, Daten und Steuersignale der dRAMs zu

legen.

Für alle U 2164 D wurden IS-Fassungen eingesetzt, um einmal die

Bausteine zu schützen bzw. sie später eventuell durch

256-KByte-RAM-Schaltkreise austauschen zu können. Ein Test des

Speichers erfolgt vorab durch mehrmaliges Lesen der

Checksumme von 2000H bis FFFFH. Sollte sich zeigen, daß sich

diese nach jedem Lesen ändert, müssen die beiden

Kondensatoren

1 nF etwas variiert werden. Danach versucht man den Speicher zu

beschreiben. Treten dabei Fehler auf, so ist der

Schaltungsaufbau nochmals zu überprüfen. Manchmal treten aber

auch Fehler durch eine ZVE auf, die als Bastlerschaltkreis

erworben wurde. dRAMs fordern ihre Parameter und sind gegenüber

Zeitabweichungen bei Impulsen wesentlich kritischer als

statische RAMs. Läuft dann alles richtig, sollte man sich etwas

Zeit nehmen, um das in [4]

beschriebene Testprogramm

einzulesen und laufen zu lassen. Hinweise dazu findet man in dem

zitierten Beitrag,

| [1] | Kieser/Meder: Mikroprozessortechnik, VEB Verlag Technik, Berlin 1986, 3. Auflage, S. 260, 265 und 266 |

| [2] | Barthels, E.: Ein 32-KByte-RAM für U-880-Mikrorechner, FUNKAMATEUR 34 (1985), H. 6, S. 306 bis 308 |

| [3] | Wolan, M.: 64-KByte-RAM-Baugruppe, radio-fernsehen-elektronik, 36 (1987), H.1, S.50 und 51 |

| [4] | Heyder, F.: Ein Speichertestprogramm für den

Amateurcomputer "AC1", FUNKAMATEUR 35 (1986), H. 12, S. 616 bis 618 |

|

|

| 44 KByte | 134 KByte |

| Bild 1 | Schaltung |

Funkamateur 06/88 |

Zum o.g. Artikel in unserem Heft 12/87. S. 615 bis 617, erreichten uns

viele Leseranfragen und Zuschriften.

Neben einigen notwendigen Korrekturen haben sich viele Leser Gedanken

gemacht, wie die Speichererweiterung

z.B. auf der 16-KByte-Zusatzspeicherplatine des "AC1" aufzubauen ist.

Unser Leser D. Herrmann,

Y37WO, stellte uns seine Erfahrungen zur Verfügung.

Aufgrund der Tatsache, daß ich meinen "AC1" mit der

64-KByte-Speichererweiterung aufgerüstet habe und

nunmehr erfolgreich testen konnte, möchte ich meine Erfahrungen

hierbei auch anderen Lesern mitteilen.

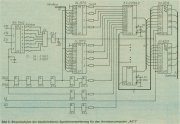

In der Schaltung gab es zunächst einige Fehler zu beseitigen. Die

Ausgänge DO der dRAM D8 bis D15 müssen an

die Eingänge A1 bis A4 von D16 und D17 gelegt werden. Für DIR

= L ist als Datenrichtung die von A nach B

definiert, d.h., die dRAM werden ausgelesen. Die Eingänge DI der

dRAM D8 bis D15 müssen an die Ausgänge

Y1 bis Y4 von D16 und D17 gelegt werden. Für DIR = H ist die

Datenrichtung von B nach Y definiert, d.h.,

die dRAM werden beschrieben. Da es sich im genannten Beitrag um eine

Erweiterung des "AC1" handelt und auch

im Text auf die Ausblendung der ersten 8 KByte verwiesen wird

(Grund-RAM/ROM), sind doch im Stromlaufplan

alle Ausgänge des MH 7442 beschaltet. Das.führt dazu,

daß eben die CPU nur den Grund-RAM-Bereich erkennt.

Zur Fehlerbeseitigung ist die Brücke am Pin 9 des MH 7442 zu

entfernen. An den Multiplexem D6 und D7 ist

die Anschaltung des Adreßbusses zu ändern. Richtig ist

folgende Adreß-Reihenfolge (von oben nach unten):

beginnend bei A0

D6 A8, A9, A10, A11

D7 A12, A13, A14, A15

beginnend bei B0

D6 A0, A1, A2, A3

D7 A4, A5, A6, A7

Die Speichererweiterung benutzt folgende Kontakte des Systembusses:

/A13 an A37; /A14 an B38; /A15 an A38; /MREQ an B9; /RFSH an A15; /RD

an A8; /WR an A9.

Ich habe die Leiterplatte der 16-KByte-Erweiterung des "AC1" benutzt. Die für die 64-K-Variante zusätzlich notwendigen Bauelemente wurden durch nachträgliches Bohren auf der Bauelementeseite untergebracht und auf der Leiterseite sauber handverdrahtet. Zum Einsatz kamen dRAM des Typs U 2164 C 20, die auf Fassungen sitzen und die jeweils mit 100 nF abgeblockt sind. Nach der Beseitigung der o.g. Fehler funktionierte die Erweiterung sofort. Der "AC1" meldet sich dabei wie gewohnt. Mehrere CRC-Prüfsummenbildungen über Teilbereiche oder den gesamten 64-K-Speicherbereich brachten aber immer wieder Abweichungen. Daraufhin wurde die Stromversorgung auf der Leiterseite durch dickeren Draht vermascht (sowohl masseseitig als auch bei der Betriebsspannung) und durch einen 100-µF-Tantal-Elko nahe den dRAM gestützt. Nun entstanden keine Abweichungen der Prüfsumme mehr. Schließlich habe ich das "AC1"-Speichertestprogramm eingesetzt und damit den Speicher mehrfach auf verschiedenen Speicherbereichen getestet. Lediglich beim Refresh-Test erschienen auf allen Datenbits gemäß Tabelle des Testprogramms die Symbole "R". Dagegen half auch das Verändern der bei den l-nF-Kondensatoren nicht - ich fand bisher noch kein Mittel. Vielleicht konnten andere Leser dazu schon Erfahrungen sammeln. Zum Schluß habe ich schließlich Speicherbereiche von Kassette mit Programmen geladen und diese mehrfach verschoben (T-Befehl) und zur Ausführung gebracht, z.B. Uhrenprogramme. Es wurden keine Fehler festgestellt. Leider stand mir das 8-K- bzw. 12-K-BASIC zum Manuskriptzeitpunkt nicht zur Verfügung. Es stellt nach Aussage von Y21SO die beste Prüfmöglichkeit für eine RAM-Erweiterung dar. Insgesamt ist einzuschätzen, daß der Aufwand für einen 64-K-Speicher im Vergleich zu den 16-K- oder 32-K-Versionen optimal ist. Bleibt abzuwarten, wie störanfällig ein solcher dRAM ist. Alternativen sind jedenfalls schon in Form von CMOS-RAMs in Sicht, die man dann auch batteriegestützt betreiben kann (Basis U 6264 D). Auch sie werden in nicht ferner Zukunft für den Amateur erhältlich sein und dann stellt eine echte RAM-Floppy für den "AC1" kein unerreichbares Ziel mehr dar.