Funkamateur 02/92 |

Ein Logikanalysator kann für viele Anwendungen in der

Amateurpraxis sehr hilfreich sein, ob es nun um die Entwicklung

eigener Schaltungen, um die Fehlersuche in digitalen Systemen oder um

die Untersuchung des Verhaltens von komplexeren

Digital-Schaltungen geht.

Daß ein solcher Vorsatz nicht unbedingt hohe Kosten verursachen

muß, wenn man sich bei den technischen Daten etwas

einschränkt, beweist der im Beitrag vorgestellte

Achtkanal-Logikanalysator für Z80-Rechner, hier

softwaremäßig für

den AC1 konzipiert. Mit einem Achtkanal-Multiplexervorsatz ist auch der

Anschluß an ein einfaches Einstrahloszilloskop

möglich, um damit ebenfalls acht Kanäle gleichzeitig sichtbar

zu machen.

Für meinen konkreten Bedarf habe ich den Logikanalysator mit

folgenden technischen Daten realisiert:

- Abtastung von TTL-Pegeln mit einer Taktfrequenz von 5 MHz als zur

Zeit maximaler Abtastrate (200 ns, variabel);

- Einlesen und Zwischenspeichern der Information in einem sRAM; damit

ist eine beliebige Untersuchung des erfaßten

Signalverlaufs möglich;

- Auswertung der Signale durch einen Mikrorechner oder einen

8-Kanal-Multiplexervorsatz an einem Einstrahloszilloskop.

Ich habe den AC1 eingesetzt, für den auch die abgebildete Software

konzipiert ist - er steuert alle Funktionen des

Logikanalysators.

Das Kernstück der Schaltung bildet ein statischer RAM. Ich setzte

einen U 6516 mit einer

Zugriffszeit von 200 ns ein. Beim Einsatz schnellerer RAMs ist eine

entsprechende Erhöhung der Abtastrate des

Gesamtgeräts möglich.

Das Meßobjekt liegt im Modus "Daten schreiben" über einen

Bustreiber direkt an den Datenleitungen des sRAMs; letztere

sind im Modus "Daten lesen" zur Rechner-PIO durchgeschaltet. Die Anwahl

des jeweiligen Datentreibers erfolgt durch den

Schalter S2 bzw. eine Leitung des PIO-Ports B über ein statisches

RS-Flipflop, das den entsprechenden Bustreiber freigibt.

Die notwendige Taktfrequenz von 20 MHz erzeugt ein Taktgenerator nebst

nachfolgender Teilerkette. Mit S1 ist der

Taktgenerator abschaltbar (z.B. zur Einspeisung eines externen Takts).

Mit Schalter S3 ist die Abtastrate einstellbar.

Über eine Steuerlogik gelangt das so ausgewählte Signal zum

Adressenzähler, der die Adressen A0 bis A10 für den RAM

und A11 für die Statussignalisierung bildet.

Die Signale "RESET" und "Start" werden vom Rechner über zwei

weitere Leitungen des PIO-Ports B gesteuert.

Der monostabile Multivibrator dient lediglich zur Anzeige des Schreib-

und Lesezustands für den Bediener,

da bei sehr geringen Abtastraten doch einige Zeit vergeht, bis die 2048

Meßwerte gespeichert sind.

Zum Lesen des RAM-Inhalts ist ein externer Zählimpuls an den

Eingang "Zählimpuls ext:" anzulegen. Bei Rechnerkopplung

wird dieser über die PIO ausgegeben.

Sollte es sich erforderlich machen, einen Start des Logikanalysators

beim Vorhandensein eines bestimmten, am Eingang

liegenden Datenworts vorzusehen, kann man den Eingang mit einem

8-Bit-Komparator, z.B. dem 74LS688, erweitern. Der

Komparator vergleicht dabei ein mittels DIL-Schalter vorher

einzustellendes Datenwort mit den anliegenden

Eingangsinformationen. Bei Übereinstimmung wird der Ausgang des

Komparators (A = B) L-aktiv. Diese Information wird mit

dem Eingang "Start" des Logikanalysators verknüpft, und beim

Anliegen der entsprechenden Bitfolge erfolgt der Start

des Erfassungsablaufs, der im folgenden detaillierter beschrieben

werden soll.

Nach dem manuellen Einstellen der gewünschten

Abtastrate mit S3 (Stufen zu 200 ns; 400 ns; 800 ns; 1,6 µs; 3,2

µs;

6,4 µs; 12,8 µs und 25.6 µs) und dem Einstellen des

Schalters S2 auf "Schreiben" übernimmt nun der Rechner die

Steuerung des Analysators

- auf Schreiben schalten (bzw. Status testen);

- Reset für Adreßzähler ausgeben;

- Startimpuls ausgeben;

- ständig Statusleitung abfragen (ist der RAM vollständig

beschrieben, schaltet die Leitung A11 über eine Steuerlogik

die Zählimpulse für den Adressenzähler ab; dies erkennt

der Rechner durch die Pegeländerung der Statusleitung).

Die Änderung des Pegels auf der Statusleitung hat zur Folge:

- der Rechner schaltet auf Lesen um;

- er gibt den Reset für den Adreßzähler aus;

- er liest die Information aus dem sRAM aus und

- das Impulsdiagramm der ersten 53 Byte erscheint auf dem Bildschirm.

Die Software ist, wie gesagt, für den AC1 geschrieben (das

Assemblerlisting kann bei der Redaktion gegen 2,50 DM in

Briefmarken mit plus 1,70 DM frankierten Rückumschlag angefordert

werden, damit ist eine einfache Anpassung auch an

andere Z80-Geräte möglich). Sie belegt folgenden

Speicherplatz:

2000H bis 23F3H: Programm Logikanalysator

2800H bis 2FFFH: Zwischenspeicher für den Bildinhalt

3000H bis 37FFH: Meßwertspeicher 1

3800H bis 3FFFH: Meßwertspeicher 2.

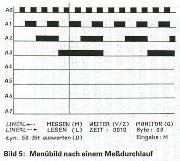

Das Programm verfügt über eine Bedienerführung, die die

Bedienung sehr vereinfacht. Nach dem Start auf Adresse 2000H

erscheint ein Menübild ähnlich Bild 5

(die dort dargestellten

Pegelverläufe erscheinen selbstverständlich erst nach

einem Meßdurchlauf).

Zunächst ist der Analysator mit dem (ausgeschalteten) Rechner

über ein 25poliges Canon-Kabel entsprechend dem

Stromlaufplan zu verbinden. Danach legen Sie die zu untersuchende

Information an den Eingang des Analysators und starten

das Programm bei 2000H. Es erscheint zunächst das Menübild.

Die Einleitung des Meßvorgangs erfolgt mit der Taste "M". Dabei

wird die Information zunächst im sRAM gespeichert. Der

Meßvorgang ist mit dem Erreichen der Adresse 2048 im

Logikanalysator-RAM beendet. Danach erfolgt das Auslesen des

Meßwertspeichers über den PIO-Port A in den Rechner.

Das Programm beginnt nun mit der Auswertung der ersten 53 Byte des

Speicherinhalts. Die Darstellung des H-Pegels erfolgt

als weißes Grafikzeichen. und der L-Pegel erscheint als

Tiefstrich. Die Auswertung der eingelesenen Informationen erfolgt

byteweise. Da bei dieser Auswertung der Meßwertspeicher 1

"zerstörend" gelesen wird, muß die Information im

Meßwertspeicher 2 für weitere Auswertungen

zwischengespeichert werden.

Mit den Tasten "V" und "Z" ist ein seitliches Verschieben vorwärts

und rückwärts im Speicher möglich. Das machte sich

erforderlich, da der AC1 nur eine Pseudografik besitzt, die lediglich

die Auswertung von gleichzeitig 53 Byte möglich macht.

Die restlichen Bildschirmpositionen je Zeile werden vom Diagrammaufbau

belegt.

Durch ein mit den Kursortasten links und rechts verschiebbares Lineal

kann man nun die gesamte Kanalinformation entlang

der senkrechten Lineallinie vergleichen. Das hierbei erfaßte Byte

(links vom Lineal) wird in der Statuszeile bei "Byte:"

in Hex-Darstellung angezeigt. Die Anzeige bei "ZEIT:" entspricht der

Stellung des Lineals im Meßintervall (1 bis 2048).

So lassen sich bei bekannten Abtastraten Zeiten zwischen bestimmten

Informationen ermitteln. Beispielsweise ergibt eine

Differenz von 3 bei einer Abtastrate von 5 MHz 600 ns Zeitdifferenz.

Durch die Betätigung der Taste "L" erfolgt ein

erneutes Auslesen des Logikanalysators. Die Taste "D" ermöglicht

eine dynamische Betriebsart des Logikanalysators mit dem

Rechner. Dabei wird ständig zwischen den Betriebsarten

Meßvorgang im Logikanalysator sowie Anzeigen der ersten 53 Byte

und

wieder zurück in den Meßvorgang usw. gesteuert. Damit kann

man besonders gut zeitkritische Vorgänge, u.a. auch bei

Abgleicharbeiten, zeitnah verfolgen.

Das Verlassen des Programms erfolgt schließlich mit "Q".

Anmerkung der Redaktion: Für MC-Programmierer bietet sich hier

auch die Möglichkeit des Abspeicherns bzw. Ladens ganzer

Speicherinhalte auf ein externes Speichermedium, um so ggf. ganze

Meßabläufe zu Vergleichs- und Demonstrationszwecken

reproduzierbar zu machen.

Ich habe die aufgebaute Schaltung zusammen mit einem

Achtkanal-Multiplexer in einem Gehäuse mit den Abmessungen

215 x 130 x 75 mm3 untergebracht und so ein kompaktes

Vielzweckgerät realisiert. Die Stromversorgung kann sowohl vom

Rechner aus als auch extern oder von der Meßschaltung her

erfolgen.

Die Verbindung zum Rechner wird mit einem 25poligen

Canon-Steckverbinder realisiert, dessen Belegung sich aus dem

Stromlaufplan Bild 1 ergibt. Um auch einen

rechnerunabhängigen

Betrieb realisieren zu können, sind

in der Frontplatte schließlich noch Schalter für Schreiben,

Lesen und je ein Taster für Reset und zum Start angebracht.

Das Leiterplattenlayout ist in den Bildern 2 und 3

gezeigt. Für

seine Entwicklung danken wir unserem

Leiterplattenhersteller, der Fa. ABCOM-electronic Leipzig.

|

|

|

| 286 KByte | 217 KByte | 202 KByte |

| Bild 1 | Bild 2 | Bild 3 |

|

|

|

| 266 KByte | 273 KByte | 39 KByte |

| Bild 4 | Listing | Bild 5 |

Funkamateur 08/92 |

Der Autor stellt zum Arbeiten mit dem Logikanalysator nach [1] eine überarbeitete Softwareversion vor.

Folgende Routinen wurden neu eingefügt:

- Kennbuchstabe: S Saven auf Kassette (Speichern einer Datei von

Adresse 3800H bis 3FFFH - Meßwertspeicher 1 - auf

ein externes Speichermedium - Kassette. Argumente ARG 1 - ARG3 werden

übergeben.)

- Kennbuchstabe: K Laden von Kassette (Die auf Kassette gespeicherte

Datei wird auf den Meßwertspeicher 1 - mit

Übergabe des Argument ARG 1 - von Kassette zurückgelesen,

kann wie in [1] beschrieben werden.)

- Kennbuchstabe: P Bildschirmkopie (Die aktuelle Bildschirmseite wird

auf einen Drucker K6313 - ausgegeben,

der Kennbuchstabe im Menübild nicht angezeigt; Umkodierung von

Grafikzeichen des Bildschirms auf druckerspezifische

Grafikzeichen.)

Zur besseren Anpassung an andere Rechnertypen wurde ein Sprungverteiler

mit den wichtigsten rechnertypischen Routinen

nach [2] eingearbeitet.

Das komplette Assemblerlisting kann bei der Redaktion bezogen werden

(mit 2,40 DM frankierter Rückumschlag sowie lose

beigelegten Briefmarken im Werte von 2,10 DM).

| [1] | Jahn, B.: Achtkanal-Logikanalysator, FUNKAMATEUR 41 (1992), H.2, S.77 |

| [2] | Heyder, F.: Der Amateurcomputer "AC1" (12) FUNKAMATEUR 34 (1985), H.1, S.40 |

|

|

|

| 89 KByte | 117 KByte | 424 KByte |

| Hardcopy | Sprungverteiler | Listing |