Funkamateur 09 und 10/86 |

Für anspruchsvolle Programme und Anwendungen, die für den

Amateurcomputer "AC1" zur Verfügung stehen,

wie den U-880-Editor/Assembler, den Texteditor, einen

8-K-Standard-BASIC-Interpreter oder ein

RTTY-Programm mit mehr Komfort und größerem Textspeicher

usw., reichen die 2 Kbyte Arbeitsspeicher

auf der Grundplatine bei weitem nicht mehr aus. Dafür ist dann

eine RAM-Speichererweiterung von

mindestens 16 Kbyte erforderlich.

Um den Aufwand, und damit natürlich die Fehlerquellen,

möglichst gering zu halten, bietet sich hier

der Einsatz von dynamischen RAM-Speicherschaltkreisen mit einer

Speicherkapazität von 16 Kbit

pro Schaltkreis an, z.B. der Typen U 256 D, K565RU3 und MH 4116. Der

preiswerte S 256 ist ebenfalls

geeignet. Wie im nachfolgenden Beitrag gezeigt wird, genügen

bereits elf Schaltkreise, um eine solche

Speichererweiterung aufzubauen, die dann einfach an den

Bus-Steckverbinder X1 des Amateurcomputers "AC1"

angesteckt wird.

Grundlage für diese Speichererweiterung bot die in

[1] veröffentlichte Lösung,

die leicht modifiziert und mit einem Leiterbild für den "AC1"-Bus

versehen wurde. Auf

eine ausführliche Beschreibung der Arbeitsweise eines

16-Kbit-dRAM-IS soll hier verzichtet werden, das

kann z.B. in [2] nachgelesen

werden.

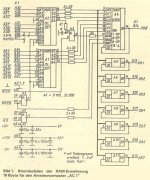

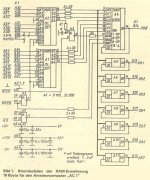

Das Schaltbild der Speichererweiterung ist in

Bild 1 dargestellt. Um den

Adreßbus der ZVE nicht weiter

zu belasten, wird auf die negierten Adreßleitungen /AB0.../AB13

zurückgegriffen. Da die Zuordnung der

ZVE-Adresse zur Speicherzellenadresse im RAM-IS, im Gegensatz z.B. zum

EPROM, selbst egal ist, bot sich

diese Lösung an. Entsprechend der Arbeitsweise des U 256 D

muß die Adreßinformation in zwei Hälften

(A0...A6 und A7...A13) dem dRAM übergeben werden. Dazu dienen die

Multiplexerschaltkreise A1 und A2.

Die Steuerung der Umschaltung der Multiplexer erfolgt mit dem durch ein

Gatter von A3 verzögertem

/MREQ-Signal der ZVE.

Das direkte /MREQ-Signal wird zum Abspeichern der Zeilenadresse (RAS)

und damit gleichzeitig zur

Realisierung des bei dRAMs notwendigen Auffrischens der Information

(Refresh) verwendet. Durch diese

einfache Lösung wird bei jedem /MREQ-Signal, also zusätzlich

zu den Refresh-Zyklen bei jedem Speicherzugriff

der ZVE, egal, ob er den Adreßbereich der RAM-Erweiterung

betrifft oder nicht, ein Auffrischen einer

Matrixzeile durchgeführt. Diese zusätzlichen und eigentlich

nicht erforderlichen Refresh-Zyklen erhöhen

die Stromaufnahme der Baugruppe etwas, aber dafür bleibt der

Aufwand minimal.

Die Spaltenadressenübergabe, und damit gleichzeitig die Auswahl

der Speichererweiterung, erfolgt mit der

Adreßleitung A14, die über den noch verbleibenden Kanal des

Multiplexers A2 an ein RC-Verzögerungsglied

geleitet und anschließend mit /RFSH verknüpft an den Eingang

zum Abspeichern der Spaltenadresse der

Speichermatrix (CAS) führt. Die Verknüpfung mit /RFSH

verhindert einen möglichen CAS-Impuls im Refresh-Zyklus.

Mit dem RC-Glied kann die RAS-CAS-Verzögerungszeit variiert und

damit den verwendeten Speicherschaltkreisen

und deren Zugriffszeit sowie den Toleranzen der Gatterlaufzeiten von A2

und A3 angepaßt werden. Meist

ist ein Kondensator von 1 nF ausreichend, ansonsten muß, da

Meßmittel oder Datenblätter der im einzelnen

verwendeten RAM-Speicher-IS oft nicht greifbar sind, der

Kapazitätswert schrittweise bis maximal 2 nF erhöht

werden. Für diesen Kondensator dürfen natürlich nur

solche Bauformen verwendet werden, die geringe Toleranz

und geringen Temperaturgang aufweisen.

Aufgrund der vereinfachten und unvollständigen

Adreßdekodierung durch A14 belegt diese Speichererweiterung

den Adreßbereich 4000H...7FFFH und gleichzeitig den Bereich von

C000H...0FFFFH. Solange das die einzige

Speichererweiterung bleibt, schadet eine solche Doppeldeutigkeit kaum.

Sollen dann später mehrere solcher

Bausteine, oder andere Speichererweiterungen zusätzlich zur

Anwendung kommen, ist eine exakte Dekodierung

erforderlich. Dem wird durch die neu definierte Busleitung RAMCS

(X1:B17) Rechnung getragen, die dann

anstelle von A14 an den Multiplexereingang gelegt wird.

Das hat den Vorteil, daß der Aufwand einer exakten Dekodierung

erst dann notwendig wird, wenn mehrere

Speichererweiterungen zum Einsatz gelangen. Außerdem kann dann

eine solche Dekodierung auf einer zentralen

Busverteilerkarte angeordnet werden, um nicht auf jeder einzelnen Karte

den Aufwand treiben zu müssen.

Die Adresse einer hier beschriebenen Speichererweiterung wäre dann

nur von ihrem Steckplatz auf der

Verteilerkarte abhängig.

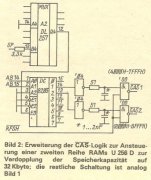

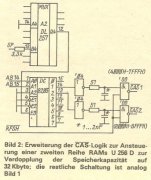

Es besteht auch die Möglichkeit, mit der gezeigten Ansteuerlogik

(A1 bis A3) und einer exakten Dekodierung

mehrere Speicherfelder mit U 256 D auf einer Karte zu betreiben. Die

dafür notwendigen Veränderungen sind im

Bild 2 dargestellt. Diese

Schaltung ist ebenfalls erprobt, aber eine Leiterplatte wurde

dafür nicht entworfen.

Die Ansteuerung des Schreibeinganges der Speicher-IS erfolgt mit dem

negierten /RD-Signal der ZVE und

nicht mit dem /WR-Signal. Mit dem hier verwendeten "Early-Write-Mode"

ist es möglich, die Anschlüsse DI

und DO des jeweiligen Speicher-IS mit dem Datenbus direkt zu verbinden,

da dadurch die Ausgangstreiber

der dRAMs nur im Lesezyklus aktiviert werden.

Zur Vermeidung von Reflexionen sind in die Adreß- und

Steuerleitungen des RAM-Feldes Widerstände 33 Ω eingefügt.

Diese Widerstände sind im Bereich 22 bis 39 Ω unkritisch [2], [3]

, in

[1] wurde ganz darauf

verzichtet.

Aufgrund der dynamischen Arbeitsweise der RAM-IS muß der Stromversorgung des Speicherfeldes besondere Aufmerksamkeit geschenkt werden, da speziell auf den +12-V- und -5-V-Leitungen Stromspitzen bis zu 100 mA je IS [3] auftreten können. Deshalb müssen alle Spannungs- und Masseleitungen möglichst induktivitätsarm ausgeführt werden. Bei +12 V und -5 V ist pro IS mit je einem Scheibenkondensator 100 nF abzublocken. Dementsprechend wird wohl eine wilde Verdrahtung des Speicherfeldes, wie sie sonst bei anderen Computerbaugruppen ohne weiteres möglich ist, kaum zum Erfolg führen. Die Versuchsschaltung wurde zwar auch auf einer Universalleiterplatte aufgebaut, das Speicherfeld jedoch ähnlich der endgültigen Leiterzugführung realisiert, wie sie in Bild 3 und 4 gezeigt wird. Die Leiterplatte ist zweilagig gestaltet.

Nachdem man die Leiterplatte noch einmal einer genauen

Sichtprüfung, besonders an den Stellen der

Bestückungsseite, die dann unter den Bauelementen liegen,

unterzogen hat, kann mit der Bestückung

aller passiven Bauelemente sowie der Logikschaltkreise A1 bis A3

begonnen werden. Der Bestückungsplan

der Leiterplatte ist im Bild 5

dargestellt. Für die Speicherschaltkreise sollte man Fassungen

verwenden,

auch wenn die Lötstellen an ihnen auf der Bestückungsseite

etwas komplizierter werden. Erstens erleichtert

das die Inbetriebnahme und die eventuelle Fehlersuche und zweitens

ermöglicht es, diese Leiterplatte dann

später mit einigen Änderungen zum Aufbau eines 64-Kbyte-dRAM

zu verwenden, ohne dann die 16-Kbit-Speicher

zerstören zu müssen. Es hat sich auch gezeigt, daß

diese Speicherschaltkreise stellenweise sehr empfindlich

gegenüber Handlötungen reagieren.

Wenn man damit fertig ist, kann man die Speichererweiterung an den Bus

stecken. Sollte sich nun der

"AC1" nicht mehr wie gewohnt nach dem Einschalten melden oder sollten

irgendwelche Fehlfunktionen auftreten,

ist noch ein Fehler vorhanden, der meist schon durch genaue Kontrolle

zu finden ist. Eigentlich kommen

dafür nur Kurzschlüsse in Frage. Ist alles in Ordnung, wird

das RAM-Feld überprüft. Zuerst werden mit

einem Vielfachmesser an jedem Speicher-IS die Betriebsspannungen und

die Masse kontrolliert, danach werden

die restlichen Pins mit dem Prüfstift angetastet. Auf allen

Adreßleitungen, RAS und WE sind Impulse nachzuweisen.

Wird zusätzlich der verbotene Bereich angezeigt, so sind meist

Kurzschlüsse zwischen benachbarten Leitungen

vorhanden. CAS muß High-Pegel zeigen, und erst wenn z.B. D 4000

7FFF "cr" eingegeben wird, müssen während

des Auslistens Impulse erscheinen. Auf den DI- bzw. DO-Leitungen

müssen ebenfalls Impulse nachweisbar sein.

Hier sind auch zusätzlich verbotene Zustände erlaubt.

Ist soweit alles in Ordnung, können die Speicherschaltkreise

aufgesteckt werden, natürlich bei ausgeschaltetem

Gerät.

Zu Beginn wird nur A4 aufgesteckt und mit dem M-Befehl getestet, ob

sich das Bit 0 auf Null und 1 setzen läßt.

Geht das, folgen die restlichen Speicher-IS. Nach wie vor darf sich an

dem Einschaltverhalten und den sonst

gewohnten Funktionen des "AC1" nichts ändern. Die Stromaufnahme

bei +12 V schwankt zwischen 25 mA im nicht

selektierten Zustand (CAS = High) und etwa 80 bis 150 mA im

angewählten Zustand (z.B. im D- oder C-Befehl).

Bei -5 V ist statisch etwa 1 mA zu messen, bei +5 V hängt die

Stromaufnahme von den verwendeten Logik-IS

(TTL oder LSTTL) ab.

Als Grobtest können nun mit dem P oder M-Befehl

ausgewählte Bitmuster wie 00, FF, AA, 55, 01, 02, 04, 08, 10, ...

, FE, FD usw. geprüft werden. Es ist auch möglich, den

Speicher mit 00 aufzufüllen und dann z.B.

ab 4000H eine Zeile 00 01 02 03 04 ... 0E 0F einzugeben. Mit Hilfe des

D- oder C-Befehls ist dann zu prüfen,

daß keine weitere Zelle ein von 00 abweichendes Muster hat und

die eingegebene Zeile nach wie vor vorhanden ist.

Treten zyklische Wiederholungen auf, kann z.B. eine Unterbrechung in

einer Adreßleitung des Speicherfeldes

vorliegen. Eine weitere Testmöglichkeit bietet z.B. diese

Kommandofolge:

P 4000 7FFF 00

T 0 4000 1000

C:

C 5000 5001 2FFF

Die letzten beiden C-Befehle dürfen bei intaktem Speicher keine

Fehlermeldungen ausgeben. Treten unregelmäßige

Fehler auf, kann der Kondensator im RC-Glied noch zu klein sein. Eine

bessere und komfortablere Testhilfe

bietet ein RAM-Testprogramm. Ein solches wird in einer der

nächsten Folgen für den "AC1" vorgestellt.

Auch die einwandfreie Funktion des 8K-BASIC-Interpreters hat sich als

brauchbares Kriterium für einen

funktionstüchtigen dRAM erwiesen. Sollten alle

Schreib/Lese-Operationen funktionieren und es bei Abarbeitung

eines Programmes, welches in den dRAM geladen wurde, Probleme geben, so

ist ebenfalls der Wert des

Kondensators zu verändern.

Diese Schaltung wurde im Zeitraum von etwas mehr als einem Jahr bereits

vielfach aufgebaut und getestet.

Sie hat sich als unkritisch und nachbausicher erwiesen. Alle Fehler

waren mit dem Prüfstift, einem

Vielfachmesser oder dem "AC1" selbst zu finden. Auch die Kaskadierung

mehrerer solcher Platten auf

einer speziellen Verteilerplatte und die Bestückung einer

Leiterplatte mit Speicherschaltkreisen

verschiedener Hersteller, bzw. auch mit S 256, wurden erfolgreich

getestet.

Abschließend sei darauf verwiesen, daß bei der Verwendung

von dynamischen Speichern der ordnungsgemäße

Refresh gewährleistet sein muß. Da die hier vorgestellte

Schaltung auf die Refresh-Erzeugung der

U-880-ZVE aufbaut, darf diese z.B. nicht für längere Zeit in

den WAIT-Zustand geschickt werden.

Auch der RESET-Impuls im "AC1" entspricht nicht den Anforderungen der

dRAMs, da er weder zeitlich begrenzt

noch M1-synchron ist. Da die RESET-Taste aber nur als

äußerste Notbremse zu verstehen sein sollte,

kann man auch diesen Kompromiß in Kauf nehmen. Ansonsten ist die

RESET-Schaltung entsprechend zu

modifizieren.

8 Stück dRAM-IS - U 256 D; S 256; K 565 RU 3

2 Stück 4fach - 2-auf-1-Multiplexer - DL 257 D; 74 LS 157; 74157

1 Stück 4 NAND-Gatter mit je 2 Eingängen - DL 000 D; PL 000;

(bei -5-V-Erzeugung D 100 D!)

Widerstände - 10 x 33 Ω 1 x 51 Ω

Kondensatoren - 16 x 100 nF; 3 x 10 µF/16 V; 1 x 33 nF; 1 x 1nF

1 Stück EFS-Stecker, 90polig

| [1] | Mrácek, K.: 16-Kbit-Zusatzspeicher (RAM) zum "ZX 81" Amatérske Radio, Ausgabe A, 33 (1984), H. 12, S. 457 bis 459 |

| [2] | Bürger, B.: Halbleiterspeicher, Teil 2 - sRAM und dRAM, Heft 30 der Reihe "Mikroelektronik - Information - Applikation, VEB HFO/BV KdT Frankfurt (Oder) 1986 |

| [3] | Oettle/Reichler: Dynamische Speicher, Zeitschrift "mc", Heft 3/1981 und Heft 4/1981 |

|

|

| 100 KByte | 35 KByte |

| Bild 1 | Bild 2 |

|

|

|

| 76 KByte | 62 KByte | 64 KByte |

| Bild 3 | Bild 4 | Bild 5 |